A imaginative and prescient for future processors with almost double the density of transistors is starting to take form, now that every one three superior chipmakers have demonstrated CFETS, or complementary field-effect transistors. CFETs are a single construction that stacks each the kinds of transistors wanted for CMOS logic. On the IEEE Worldwide Electron Gadgets Assembly this week in San Francisco, Intel, Samsung, and TSMC confirmed what progress they’ve made towards the subsequent evolution in transistors.

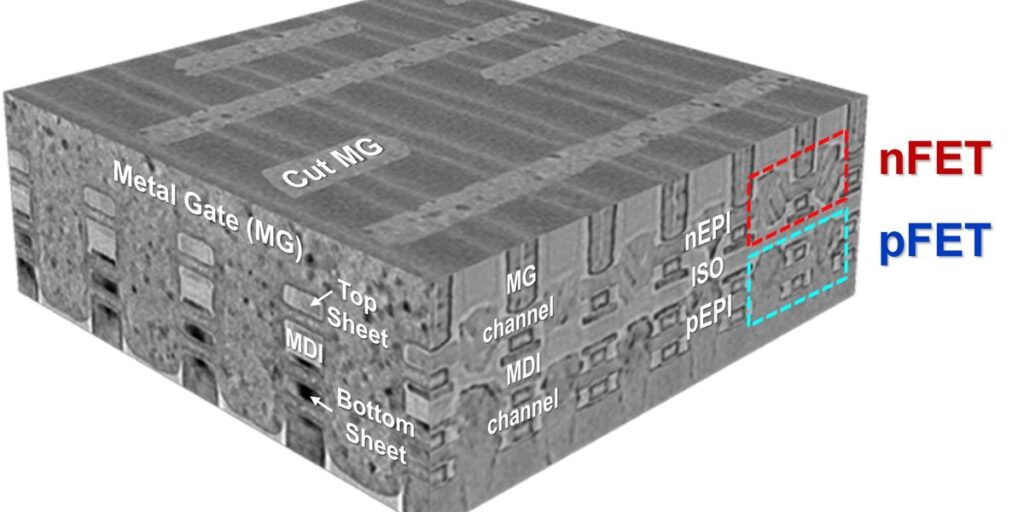

Chip firms are transitioning from the FinFET machine construction in use since 2011 to nanosheet, or gate-all-around, transistors. The names replicate the fundamental construction of the transistor. Within the FinFET, the gate controls the stream of present by a vertical silicon fin. Within the nanosheet machine, that fin is minimize right into a set of ribbons, every of which is surrounded by the gate. The CFET basically takes a taller stack of ribbons and makes use of half for one machine and half for the opposite. This machine, as Intel engineers defined within the December 2022 challenge of IEEE Spectrum, builds the 2 kinds of transistor—nFETs and pFETs—on prime of one another in a single, built-in course of.

Specialists estimate CFETs to roll out commercially seven to 10 years from now, however there may be nonetheless loads of work earlier than they’re prepared.

Intel’s inverter

Intel was earliest of the three to exhibit the CFET, unveiling an early model at IEDM again in 2020. This time round, Intel is reporting a number of enhancements surrounding the best circuit that the CFET makes, an inverter. A CMOS inverter sends the identical enter voltage to the gates of each gadgets within the stack and produces an output that’s the logical inverse of the enter.

“The inverter is finished on a single fin,” Marko Radosavljevic, principal engineer at Intel’s elements analysis group, advised reporters forward of the convention. “At most scaling, it could be 50 p.c” of the dimensions of an abnormal CMOS inverter, he stated.

Intel’s inverter circuits rely on a brand new method of connecting the highest and backside transistors [yellow] and on contacting certainly one of them from beneath the silicon [grey]Intel

The hitch is that squeezing in all of the interconnects wanted to make that two-transistor stack into an inverter circuit eats away on the space benefit. To maintain issues tight, Intel tried to take away among the congestion concerned in connecting to the stacked machine. In at the moment’s transistors, all of the connections come from above the machine itself. However later this 12 months, Intel is deploying a expertise known as bottom energy supply that enables interconnects to exist each above and beneath the floor of the silicon. Utilizing that expertise to contact the underside transistor from beneath as an alternative of from above considerably simplified the circuit. The ensuing inverter had a density high quality known as contacted poly pitch (CPP, basically the minimal distance from one transistor gate to the subsequent) of 60 nanometers. Right this moment’s 5 nm node chips have a CPP of about 50 nm.

Moreover, Intel improved the CFET stack’s electrical traits by rising the variety of nanosheets per machine from two to a few, lowering the separation between the 2 gadgets from 50 nm to 30 nm, and utilizing an improved geometry for connecting elements of the machine.

Samsung’s secret sauce

Samsung went even smaller than Intel, displaying outcomes for 48-nm and 45-nm contacted poly pitch (CPP), in comparison with Intel’s 60 nm, although these had been for particular person gadgets, not full inverters. Though there was some efficiency degradation within the smaller of Samsung’s two prototype CFETs, it wasn’t a lot, and the corporate’s researchers imagine manufacturing course of optimization will deal with it.

Essential to Samsung’s success was the power to electrically isolate the sources and drains of the stacked pFET and nFET gadgets. With out sufficient isolation, the machine, which Samsung calls a 3D stacked FET (3DSFET), will leak present. A key step to reaching that isolation was swapping an etching step involving moist chemical compounds with a brand new type of dry etch. That led to an 80 p.c increase within the yield of excellent gadgets.

Like Intel, Samsung contacted the underside of the machine from beneath the silicon to save lots of house. Nonetheless, the Korean chipmaker differed from the American one through the use of a single nanosheet in every of the paired gadgets, as an alternative of Intel’s three. Based on its researchers, rising the variety of nanosheets will improve the CFET’s efficiency.

TSMC takes its shot

Like Samsung, TSMC too managed to get to an industrially-relevant pitch of 48 nm. Its machine’s distinctions included a brand new method to kind a dielectric layer between the highest and backside gadgets to maintain them remoted. Nanosheets are usually shaped from alternating layers of silicon and silicon germanium. On the acceptable step within the course of, a silicon-germanium particular etching technique removes that materials, releasing the silicon nanowires. For the layer destined to isolate the 2 machine from one another, TSMC used silicon germanium with an unusually excessive fraction of germanium, understanding that it could etch away sooner than the opposite SiGe layers. That method the isolation layer could possibly be constructed a number of steps earlier than releasing the silicon nanowires.

From Your Web site Articles

Associated Articles Across the Net